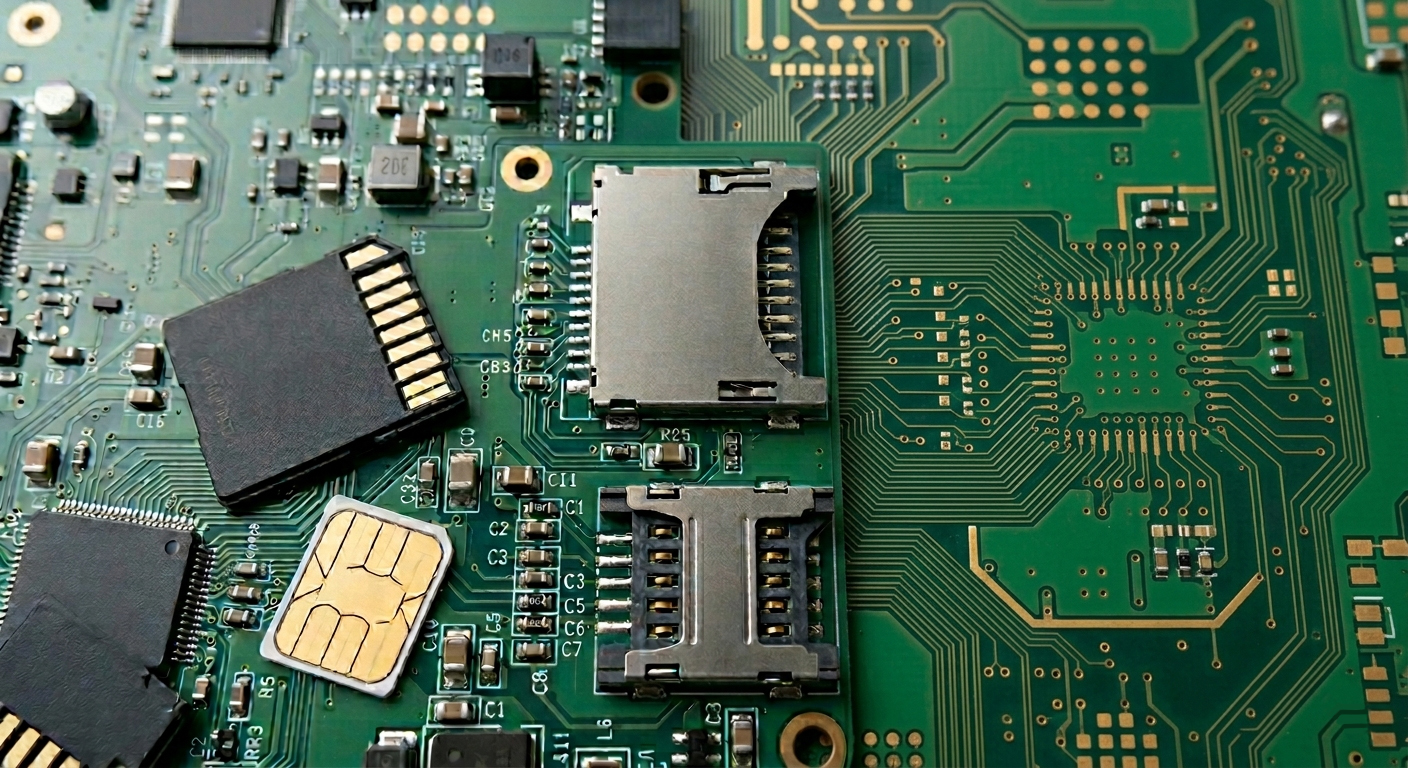

數位連結的隱形基石:Micro SD 與 Nano SIM 卡槽引腳定義與 SMT 設計深度解析

在智慧型手機、工業嵌入式系統及邊緣運算設備的設計中,SD 卡(大容量儲存) 與 SIM 卡(身分識別) 是兩大最核心的外部介面。雖然兩者在外觀上不斷微型化(如 Nano SIM 與 Micro SD),但其內部的 引腳定義 (Pinout) 與電氣特性卻有著本質上的區別。本文將拆解主流 4FF 標準與 UHS 介面的設計要點。

一、 Micro SD (TF) 卡槽:支援 UHS 高速數據傳輸的物理通道

Micro SD 卡採用串列傳輸協議,標準引腳數為 8 Pin(在 UHS-I 模式下)。其引腳配置不僅負責供電,更透過 4-bit 數據線達成高速讀寫效能。

Micro SD (UHS-I) 引腳定義詳細表

|

引腳編號 |

名稱 |

功能描述 |

技術備註與設計建議 |

|

Pin 1 |

DAT2 |

數據線第 2 位 |

支援 4-bit 寬頻傳輸模式 |

|

Pin 2 |

CD/DAT3 |

卡片偵測 / 數據線第 3 位 |

兼具片選(CS)功能(SPI 模式下) |

|

Pin 3 |

CMD |

命令 / 回應通道 |

傳輸控制指令與握手協議的核心 |

|

Pin 4 |

VDD |

正供應電源 |

通常為 3.3V(UHS 模式可降至 1.8V 以省電) |

|

Pin 5 |

CLK |

時鐘訊號 (Clock) |

決定同步頻率,需嚴格控管抖動 (Jitter) |

|

Pin 6 |

VSS |

接地 (GND) |

電路迴路參考點,建議加寬走線 |

|

Pin 7 |

DAT0 |

數據線第 0 位 |

基本數據傳輸線(預設啟動線) |

|

Pin 8 |

DAT1 |

數據線第 1 位 |

支援 4-bit 寬頻傳輸模式 |

Layout 關鍵: 在 PCB 佈線時,DAT0-DAT3 與 CLK、CMD 屬於極高速訊號線,必須嚴格遵守等長走線 (Length Matching) 與包地處理,並在靠近卡槽處增加 ESD 保護元件,以防止靜電或電磁干擾(EMI)導致讀寫失敗。

二、 Nano SIM 卡槽 (4FF):安全認證與動態電源管理

相對於 SD 卡的高速需求,Nano SIM 卡(4FF 標準)的引腳定義更側重於邏輯穩定性與電源切換。其運作邏輯嚴格遵循 ISO 7816-3 異步傳輸標準。

Nano SIM (4FF) 引腳定義詳細表

|

引腳編號 |

名稱 |

功能描述 |

技術備註 |

|

C1 |

VCC |

供應電源 |

支援 1.8V / 3.0V 自動偵測與切換 |

|

C2 |

RST |

重置訊號 |

用於初始化卡片內部的安全處理器 |

|

C3 |

CLK |

時鐘訊號 |

由讀卡控制器提供同步時脈(通常 < 5MHz) |

|

C5 |

GND |

接地 (GND) |

系統參考地,需確保低阻抗連接 |

|

C6 |

VPP |

編程電壓 |

現代 SIM 卡多已不使用(通常懸空或接 VCC) |

|

C7 |

I/O |

數據輸入 / 輸出 |

單線半雙工異步傳輸 (Half-duplex) |

機構設計重點: SIM 卡槽通常具備一個額外的偵測引腳 (CD - Card Detect),這不屬於卡片觸點,而是插槽機構的一部分。當卡托完全插入時,引腳狀態改變會觸發系統中斷,實現熱插拔 (Hot-swap) 的邏輯判斷。

專業 Q&A 區塊:卡槽設計常見技術痛點解答

Q1:為什麼 Micro SD 卡在高頻讀寫時容易掉線?

A:這通常與電源完整性 (Power Integrity) 或 阻抗不匹配有關。建議在 VDD 引腳附近放置 0.1μF 與 10μF的去耦電容,並確保訊號線阻抗控制在50Ω左右,以減少反射波干擾。

Q2:如何優化 SIM 卡槽的防靜電 (ESD) 性能?

A:由於卡槽開口直接暴露於外部,建議在 C1 (VCC)、C2 (RST)、C3 (CLK) 與 C7 (I/O) 線路上佈置低電容值(< 1pF)的 TVS 瞬態電壓抑制二極體,且 TVS 應盡可能靠近卡槽物理開口處。

Q3:Push-Push 型與彈盤型 (Tray) 卡槽在應用上有何差異?

A:Push-Push(自彈式) 適合需要頻繁手動更換卡片的外部裝置,但抗震性較弱;Tray(卡托式) 則常見於手機與嵌入式工業電腦,其結構緊湊且抗震性佳,適合空間受限或高振動環境。

精準佈局,連結穩定未來

理解 Micro SD 與 Nano SIM 卡槽的引腳定義,是開發穩健電子產品的第一步。SD 卡負責大容量數據的「快」,而 SIM 卡負責身分驗證的「穩」。確保這兩類介面的硬體佈局精準、熱管理到位且具備足夠的電氣保護,才能為使用者提供無縫且安全的數位體驗。